Bamboozled by Bit Errors?

Modern high-speed links for the fastest Ethernet rates of 400GbE and above use PAM-4 electrical modulation. This modulation format allows interfaces to run at the speeds required for 400GbE and above, but PAM-4 modulation is more susceptible to the impacts of noise and signal integrity. This is mitigated by the use of forward error correction (FEC) coding, which is integrated into the Ethernet stack. Even with FEC, it is critical to understand all the errors in a link as some may indicate marginal product performance or even a significant design flaw.

Conventional test equipment can count bit errors, but this gives no insight into the nature of the errors. Engineers are blindly troubleshooting and laboring to understand the real issues and may even completely miss a fundamental design flaw. VIAVI has developed comprehensive and integrated tool sets that give clear indication into magnitude of the errors and deep insight into their nature to help resolve things more quickly.

Why BER Doesn’t Help

Bit error rate is a coarse measurement. It basically tells you how many bits are in error over a time interval. Even with fine time granularity, you can still be looking at billions of bits, and the basic bit error rate (BER) doesn’t help in understanding how the errors are distributed and if they actually are a cause for concern.

The first place to start is looking at the FEC errored symbols per codeword profile.

The two examples below were generated on equipment, that when tested with a conventional BER tester, gave very similar results. But when examined using the VIAVI ONT-800 FEC errored symbols view, a very different picture emerges.

Case 1 (left) – A ‘good’ FEC tail with rapid fall-off of errored symbols per codeword

Case 2 (right) – A ‘bad’ FEC tail with a long tail leading to uncorrectable codewords and dropped packets

Both the above images occur at approximately the same BER. A simple BERT would not show any significant difference between the two cases so a simple pass/fail threshold would allow bad parts to be used! The VIAVI errored symbols per codeword view gives critical information at a glance. The length and shape of the tail can quickly give the experienced engineer a lot of information. A short tail with a rapid monotonic fall off to zero errored symbols above the 5 counts (after a reasonable run time) is a result which would give no major concern, but extended and non-monotonic tails must be investigated further.

The next stage is to understand why there are so many errored symbols in Case 2.

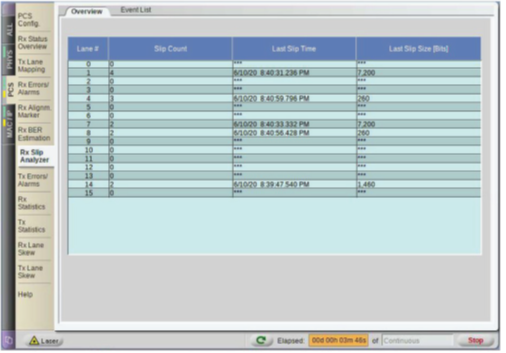

The VIAVI ONT family offers several unique tools to dig into this. The ONT can track the error profile and detect error bursts and bit slips – a potential cause of ‘bad’ FEC tails.

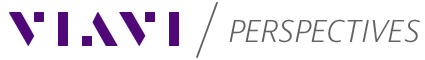

VIAVI ONT-800 bit slip view

The RX slip analysis view quickly identifies issues with several of the logical lanes having significant bit slips. This would cause the bad FEC tail we see in Case 2.

The designer can then make appropriate changes (this could include altering TX equalizer settings and updating DSP firmware).

To further ensure design robustness, the user can stress the link with the ONT Dynamic Skew feature. This maximizes the chance of crosstalk, and also stresses modern DSP based CDRs and equalizers to ensure they have enough operating margin.

Instant and Complete Error Identification

Without the right insight, and relying on simple BER, you will miss significant issues with modern high-speed Ethernet ICs, modules and systems. Only a view which instantly highlights the impact of the error profile and gives insight into the ‘error fingerprint’ can help with PAM-4 based interfaces.

The VIAVI ONT family has all this integrated to help validate and debug PAM-4, and prevent you from being bamboozled by bit errors!

The VIAVI ONT-800 provides deep measurements and instant insights

VIAVI Can Help!

To get an insightful view of your high-speed optical module performance using testing solutions that meet the highest industry standards—speak to our VIAVI applications team.

Also, please read our other recent blogs: When ‘Just Good Enough’ isn’t Good Enough, Integrated Testing Simplifies DCO Complexities, What’s All the 800G Stuff? Evolution, Revolution…or Both?, and What’s All This Error Fingerprint Stuff?,